Desain tinafotoniksirkuit terpadu

Sirkuit terpadu fotonik(PIC) sering dirancang kalayan bantosan skrip matematika kusabab pentingna panjang jalur dina interferometer atanapi aplikasi sanés anu sénsitip kana panjang jalur.PICdijieun ku cara ngalapis sababaraha lapisan (biasana 10 dugi ka 30) dina wafer, anu diwangun ku seueur bentuk poligonal, anu sering digambarkeun dina format GDSII. Sateuacan ngirim file ka produsén photomask, disarankeun pisan pikeun tiasa ngasimulasikeun PIC pikeun mastikeun leresna desain. Simulasi dibagi kana sababaraha tingkatan: tingkat anu panghandapna nyaéta simulasi éléktromagnétik (EM) tilu diménsi, dimana simulasi dilakukeun dina tingkat sub-panjang gelombang, sanaos interaksi antara atom dina bahan diurus dina skala makroskopis. Métode anu umum kalebet domain Waktu bédana-terhingga tilu diménsi (3D FDTD) sareng ékspansi eigenmode (EME). Métode ieu paling akurat, tapi teu praktis pikeun sakabéh waktos simulasi PIC. Tingkat salajengna nyaéta simulasi EM 2,5 diménsi, sapertos rambatan sinar bédana-terhingga (FD-BPM). Métode ieu langkung gancang, tapi ngorbankeun sababaraha akurasi sareng ngan ukur tiasa nanganan rambatan paraksial sareng teu tiasa dianggo pikeun ngasimulasikeun resonator, contona. Tingkat salajengna nyaéta simulasi EM 2D, sapertos 2D FDTD sareng 2D BPM. Ieu ogé langkung gancang, tapi gaduh fungsi anu terbatas, sapertos henteu tiasa ngasimulasikeun rotator polarisasi. Tingkat salajengna nyaéta simulasi matriks transmisi sareng/atanapi hamburan. Unggal komponén utama dikirangan janten komponén kalayan input sareng output, sareng waveguide anu nyambung dikirangan janten élémen pergeseran fase sareng atenuasi. Simulasi ieu gancang pisan. Sinyal kaluaran diala ku cara ngalikeun matriks transmisi ku sinyal input. Matriks hamburan (anu élémenna disebut parameter-S) ngalikeun sinyal input sareng output dina hiji sisi pikeun mendakan sinyal input sareng output di sisi anu sanés tina komponén. Dasarna, matriks hamburan ngandung pantulan di jero élémen. Matriks hamburan biasana dua kali langkung ageung tibatan matriks transmisi dina unggal diménsi. Singkatna, tina EM 3D dugi ka simulasi matriks transmisi/hamburan, unggal lapisan simulasi nampilkeun trade-off antara kecepatan sareng akurasi, sareng désainer milih tingkat simulasi anu pas pikeun kabutuhan khususna pikeun ngaoptimalkeun prosés validasi desain.

Nanging, ngandelkeun simulasi éléktromagnétik tina unsur-unsur anu tangtu sareng nganggo matriks panyebaran/transfer pikeun simulasi sadaya PIC henteu ngajamin desain anu leres pisan di payuneun pelat aliran. Salaku conto, panjang jalur anu salah itungan, pandu gelombang multimode anu gagal sacara efektif ngurangan mode orde tinggi, atanapi dua pandu gelombang anu caket teuing silih anu ngarah kana masalah gandengan anu teu kaduga kamungkinan moal kadeteksi nalika simulasi. Ku alatan éta, sanaos alat simulasi canggih nyayogikeun kamampuan validasi desain anu kuat, éta tetep meryogikeun tingkat waspada anu luhur sareng pamariksaan anu ati-ati ku desainer, digabungkeun sareng pangalaman praktis sareng pangaweruh téknis, pikeun mastikeun akurasi sareng reliabilitas desain sareng ngirangan résiko lambaran aliran.

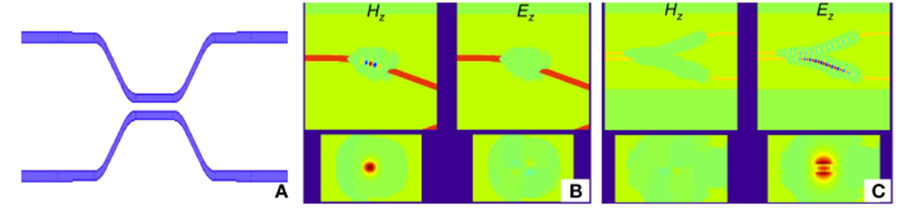

Téhnik anu disebut sparse FDTD ngamungkinkeun simulasi FDTD 3D sareng 2D dilakukeun langsung dina desain PIC anu lengkep pikeun validasi desain. Sanaos hésé pikeun alat simulasi éléktromagnétik pikeun simulasi PIC skala anu ageung pisan, sparse FDTD tiasa simulasi daérah lokal anu lumayan ageung. Dina FDTD 3D tradisional, simulasi dimimitian ku inisialisasi genep komponén médan éléktromagnétik dina volume anu dikuantisasi khusus. Nalika waktos maju, komponén médan anyar dina volume diitung, sareng saterasna. Unggal léngkah meryogikeun seueur itungan, janten peryogi waktos anu lami. Dina FDTD 3D sparse, tinimbang ngitung dina unggal léngkah dina unggal titik volume, daptar komponén médan dijaga anu sacara téoritis tiasa pakait sareng volume anu ageung sacara acak sareng diitung ngan ukur pikeun komponén éta. Dina unggal léngkah waktos, titik-titik anu caket kana komponén médan ditambahkeun, sedengkeun komponén médan di handap ambang daya anu tangtu dileupaskeun. Pikeun sababaraha struktur, itungan ieu tiasa sababaraha urutan gedena langkung gancang tibatan FDTD 3D tradisional. Nanging, FDTDS anu jarang henteu tiasa dianggo kalayan saé nalika ngurus struktur dispersif sabab widang waktos ieu nyebar teuing, ngahasilkeun daptar anu panjang teuing sareng sesah diurus. Gambar 1 nunjukkeun conto cuplikan layar simulasi FDTD 3D anu sami sareng pamecah sinar polarisasi (PBS).

Gambar 1: Hasil simulasi tina FDTD sparse 3D. (A) nyaéta tampilan luhur tina struktur anu keur disimulasikeun, nyaéta coupler directional. (B) Némbongkeun cuplikan layar tina simulasi ngagunakeun éksitasi quasi-TE. Dua diagram di luhur némbongkeun tampilan luhur tina sinyal quasi-TE sareng quasi-TM, sareng dua diagram di handap némbongkeun tampilan cross-sectional anu saluyu. (C) Némbongkeun cuplikan layar tina simulasi ngagunakeun éksitasi quasi-TM.

Waktos posting: 23-Jul-2024